# Dual-Path Hybrid Synchronous Rectifier in Active Clamp Forward Converter for Inductor Current Reduction

Katsuhiro Hata<sup>1</sup>, Sadanori Suzuki<sup>2</sup>, and Makoto Takamiya<sup>1</sup> <sup>1</sup>The University of Tokyo, Tokyo, Japan <sup>2</sup>Toyota Industries Corporation, Aichi, Japan E-mail: khata@iis.u-tokyo.ac.jp

*Abstract*— A dual-path hybrid synchronous rectifier (DPH-SR) in active clamp forward (ACF) converters is proposed for inductor current reduction to solve inductor cooling problems under heavy load. In the proposed DPH-SR, the flying capacitor also supplies current to the output, thereby reducing the inductor current. In the measurement, the peak efficiency of the ACF converters with the proposed DPH-SR and conventional SR was 90.9 % and 89.0 % at 10 Aout, respectively, resulting in the improvement in efficiency by 1.9 %. In addition, the inductor conduction loss of the proposed DPH-SR is reduced by 43.0 % by reducing the inductor current by 24.8 % at 20 Aout.

Keywords— Active clamp forward converter, Synchronous rectifier, Hybrid DC-DC converter, Dual-path

## I. INTRODUCTION

Active clamp forward (ACF) converters [1-2] are suitable for a high step-down conversion in applications such as EV/HEV, servers, and data centers [3-5]. Due to the conduction loss in the output inductor, however, the heat generated by the coil increases the cost of cooling. To solve the problem, rectification circuits to reduce the inductor current are beneficial for the ACF converter in high current applications.

Previous studies have proposed indirect hybrid step-down DC-DC converters [6–10], where the inductor is indirectly connected to the output, which can achieve the smaller inductor current than the output current because the output current is supplied from a dual path (inductor and capacitor path) unlike the conventional buck converter and direct hybrid converters [11–16]. Based on the circuit topologies of indirect hybrid DC-DC converters, in this paper, a dual-path hybrid synchronous rectifier (DPH-SR) for the ACF converter is proposed to reduce the inductor conduction loss by reducing the inductor current.

This paper describes the operation principle and basic characteristics of the proposed DPH-SR. In addition, the feasibility of the ACF converter with the proposed DPH-SR is demonstrated by experiments.

## II. PROPOSED DUAL-PATH HYBRID SYNVRONOUS RECTIFIER

#### A. Circuit operation and voltage conversion ratio

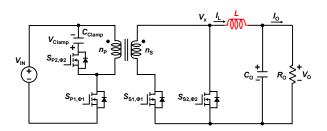

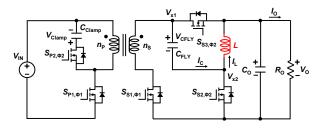

Fig. 1 shows the ACF converter with the conventional synchronous rectifier (SR). In this topology, the output current  $I_0$  is supplied through the output inductor L, which can cause inductor cooling problems under heavy load. To reduce the inductor losses, the dual-path hybrid synchronous rectifier (DPH-SR) is proposed as shown in Fig. 2. Compared to the conventional SR, the switch  $S_{S3,\Phi2}$  and the flying capacitor  $C_{FLY}$  are added in the proposed DPH-SR.

Fig. 1. Active clamp forward converter with conventional synchronous rectifier.

Fig. 2. Active clamp forward converter with proposed dual-path hybrid synchronous rectifier (DPH-SR).

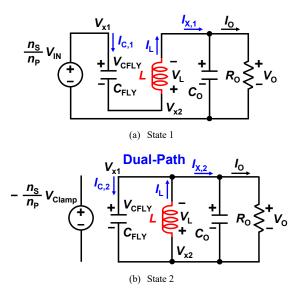

Fig. 3 shows the two circuit states in the proposed DPH-SR. Although the two switches on the primary side of the ACF converter operate in opposition to apply the AC voltage to the secondary side, the transformer supplies current to the load only during State 1. Then, the flying capacitor  $C_{FLY}$  is connected to the inductor *L* in series. On the other hand, during State 2,  $C_{FLY}$  is in parallel with *L* and  $I_0$  is supplied from the dual path, which helps to reduce the inductor DC current  $I_L$ .

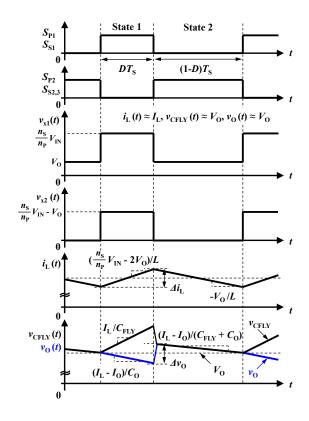

Fig. 4 shows the key operation waveforms in the proposed DPH-SR. By considering the voltage-second balance in L and the charge balance in  $C_{FLY}$  and  $C_0$  at the periodic steady state, the voltage conversion ratio M of the ACF converter with the proposed DPH-SR is expressed as follows:

$$0 = \langle V_{\rm L} \rangle$$

$$= \left(\frac{n_{\rm s}}{n_{\rm p}} V_{\rm IN} - V_{\rm CFLY} - V_{\rm O}\right) DT_{\rm s} + (0 - V_{\rm O})(1 - D)T_{\rm s}$$

$$= \left(\frac{n_{\rm s}}{n_{\rm p}} V_{\rm IN} - 2V_{\rm O}\right) DT_{\rm s} - V_{\rm O}(1 - D)T_{\rm s}$$

$$\Leftrightarrow \frac{V_{\rm O}}{V_{\rm IN}} = \frac{n_{\rm s}}{n_{\rm p}} \frac{D}{1 + D}$$

(1)

Fig. 3. Two circuit states in the proposed DPH-SR.

$$M = \frac{V_{\rm o}}{V_{\rm IN}} = \frac{n_{\rm s}}{n_{\rm p}} \frac{D}{1+D}$$

(2)

where  $V_{\text{IN}}$ ,  $V_{\text{O}}$ ,  $V_{\text{CFLY}}$ ,  $\langle V_L \rangle$ ,  $n_P$ ,  $n_S$ ,  $T_S$ , and D are the input voltage, the output voltage, the flying capacitor voltage, the average inductor voltage, the number of the transformer primary winding turns, the number of transformer secondary winding turns, the switching period, and the duty cycle, respectively.

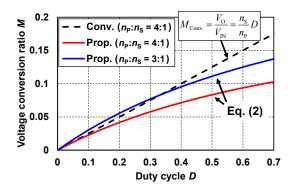

Fig. 5 illustrates M as functions of D in the ACF converter with the proposed DPH-SR and conventional SR. The proposed DPH-SR can achieve a higher step-down ratio with the same  $n_P$ ,  $n_S$ , and D as compared with the conventional SR. If a step-down ratio in the same range as that of the conventional SR is required, the proposed DPH-SR can be accommodated by redesigning the transformer turns ratio.

### B. Inductor DC current

By applying the charge balance in  $C_{FLY}$  at periodic steadystate, the total charges  $Q_{C,1}$  and  $Q_{C,2}$  flowing to  $C_{FLY}$  in each states satisfy the following equations.

$$\langle Q_{\rm C} \rangle = Q_{\rm C,1} + Q_{\rm C,2} = 0 \Leftrightarrow Q_{\rm C,1} = -Q_{\rm C,2}$$

(3)

As shown in Fig. 3(a),  $Q_{C,1}$  is determined based on the inductor current  $I_L$  because  $C_{FLY}$  is connected to the inductor L in series during State 1. Since  $Q_{C,2}$  is given by eq. (3),  $Q_{C,1}$  and  $Q_{C,2}$  can be described as follows:

$$Q_{\rm C,1} = Q_{\rm L,1} = I_{\rm L} D T_{\rm S} \tag{4}$$

$$Q_{\rm C,2} = -Q_{\rm C,1} = -I_{\rm L} DT_{\rm S} \,. \tag{5}$$

Additionally, by applying the charge balance in  $C_0$ , the average output charge  $Q_0$  is equal to the sum of the total charges  $Q_{X,1}$  and  $Q_{X,2}$  flowing to  $C_0$  during each state. As shown in Fig. 3(a),  $Q_{X,1}$  is same as  $Q_{C,1}$  because  $C_{FLY}$  and L are connected in series during State 1. On the other hand,  $Q_{X,2}$  is given by  $Q_{C,2}$  and  $Q_{L,2}$  because  $C_{FLY}$  and L are connected in

Fig. 4. Circuit operation of the proposedosed DPH-SR.

Fig. 5. Voltage conversion ratio M vs. duty cycle D.

parallel during State 2. Based on these assumptions,  $Q_0$  is obtained as follows:

$$Q_{\rm o} = Q_{\rm X,1} + Q_{\rm X,2}$$

=  $Q_{\rm C,1} + (-Q_{\rm C,2} + Q_{\rm L,2})$

=  $I_{\rm L}DT_{\rm S} + I_{\rm L}DT_{\rm S} + I_{\rm L}(1-D)T_{\rm S}$

=  $(1+D)I_{\rm L}T_{\rm s}$ . (6)

Therefore, the relationship between the output current  $I_0$  and the inductor DC current  $I_L$  in the proposed DPH-SR is expressed as follows:

$$I_{\rm O} = (1+D)I_{\rm L} \tag{7}$$

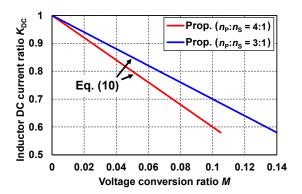

Fig. 6. Inductor DC current ratio  $K_{DC}$  vs. voltage conversion ratio M.

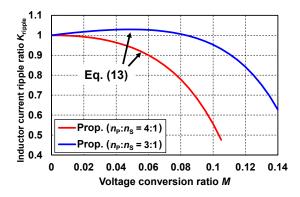

Fig. 7. Inductor current ripple ratio  $K_{ripple}$  vs. voltage conversion ratio M.

$$I_{\rm L, Prop.} = \frac{1}{1+D} I_{\rm O} = \left\{ 1 - \frac{M}{\left(n_{\rm S} / n_{\rm P}\right)} \right\} I_{\rm O} \,. \tag{8}$$

On the other hand, the inductor DC current in the conventional SR  $I_{L,Conv}$  is as follows regardless of the transformer turns ratio  $(n_S/n_P)$ .

$$I_{\rm L,Conv.} = I_{\rm O} \tag{9}$$

From eqs. (8) and (9), the inductor DC current in the proposed DPH-SR  $I_{L,Prop.}$  can be reduced thanks to the contribution of  $C_{FLY}$  to the output current in State 2, as compared with the inductor DC current in the conventional SR  $I_{L,Conv.}$  as follows:

$$K_{\rm DC} = \frac{I_{\rm L, Prop.}}{I_{\rm L, Conv.}} = 1 - \frac{M}{\left(n_{\rm S, Prop.} / n_{\rm P, Prop.}\right)}.$$

(10)

where  $n_{\text{P,Prop.}}$  and  $n_{\text{S,Prop.}}$  are the number of the primary and secondary winding turns of the transformer in the proposed DPH-SR, respectively. Therefore, the inductor DC current ratio  $K_{\text{DC}}$  depends only on the step-down ratio and the transformer turns ratio of the proposed DPH-SR.

Fig. 6 shows  $K_{DC}$  vs. M, indicating that the proposed DPH-SR can reduce  $I_L$ . Although the effect differs depending on the transformer turns ratio,  $K_{DC}$  is always less than 1 under the condition of step-down operation. Assuming the conditions of M = 0.05 and  $n_{P,Prop.} = 4:1$ , the inductor DC current can be reduced by 20% because  $K_{DC}$  is 0.8.

## C. Inductor Current Ripple

Additionally, in order to compare the inductor conduction loss of the proposed DPH-SR and conventional SR, the inductor current ripple is also analyzed.

From the inductor voltage  $V_L$  in state 2, which is shown in Fig. 3(b), the inductor current ripple of the proposed DPH-SR  $\Delta I_{L,Prop.}$  is obtained as follows:

$$\Delta I_{\text{L,Prop.}} = \frac{V_{\text{o}} T_{\text{s}}}{L} \left\{ 1 - \frac{M}{\left( n_{\text{s,Prop.}} / n_{\text{p,Prop.}} \right) - M} \right\}.$$

(11)

Similarly, the inductor current ripple of the conventional SR  $\Delta I_{L,Conv.}$  is also described as follows:

$$\Delta I_{\text{L,Conv.}} = \frac{V_{\text{o}} T_{\text{S}}}{L} \left( 1 - D \right)$$

$$= \frac{V_{\text{o}} T_{\text{S}}}{L} \left\{ 1 - \frac{M}{\left( n_{\text{S,Prop.}} / n_{\text{P,Prop.}} \right)} \right\}.$$

(12)

Since the voltage applied to L is reduced thanks to  $C_{FLY}$ , the inductor current ripple in the proposed DPH-SR can be reduced as compared with that in the conventional SR as follows:

$$K_{\text{ripple}} = \frac{\Delta I_{\text{L,Prop.}}}{\Delta I_{\text{L,Conv.}}}$$

$$= \frac{\left(n_{\text{S,Conv.}} / n_{\text{P,Conv.}}\right) \left\{ \left(n_{\text{S,Prop.}} / n_{\text{P,Prop.}}\right) - 2M \right\}}{\left\{ \left(n_{\text{S,Conv.}} / n_{\text{P,Conv.}}\right) - M \right\} \left\{ \left(n_{\text{S,Prop.}} / n_{\text{P,Prop.}}\right) - M \right\}}.$$

(13)

where  $n_{P,Conv.}$  and  $n_{S,Conv.}$  are the number of the primary and secondary winding turns of the transformer in the conventional SR, respectively. Therefore, the inductor current ripple ratio  $K_{ripple}$  depends not only on the transformer turns ratio of the proposed DPH-SR but also on that of the conventional SR.

Fig. 7 shows  $K_{\text{ripple}}$  vs. M, indicating that the inductor current ripple in the proposed DPH-SR can be reduced at any step-down ratio when using a transformer with the same turns ratio as the ACF converter with the conventional SR. Assuming the conditions of M = 0.05 and  $n_{\text{P,Prop.}} : n_{\text{S,Prop.}} =$  $n_{\text{P,Conv.}} : n_{\text{S,Conv.}} = 4:1$ , the inductor current ripple of the proposed DPH-SR is slightly improved compared to the that of the conventional SR because  $K_{\text{ripple}}$  is 15/16 = 0.9375. In addition, even if the transformer winding ratio of the proposed DPH-SR is redesigned to 3:1, the current ripple of the inductor does not deteriorate significantly.

#### III. EXPERIMENTAL VERIFICATION

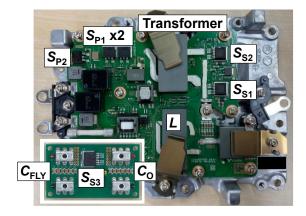

To demonstrate the feasibility of the proposed DPH-SR, the experiments were conducted using the ACF converter and additional circuit board shown in Fig. 8. The experimental conditions and selected components are listed in Table I.

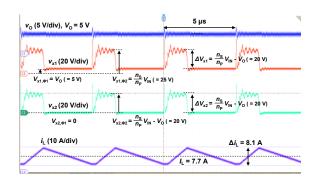

Fig. 9 shows the measured waveforms of the proposed DPH-SR at the output current  $I_0$  of 10 A, indicating that the operation shown in Fig. 4 was successfully implemented. In

Fig. 8. Active clamp forward converter and additional circuit board for the proposed DPH-SR.

| TABLE I. | CIRCUIT COMPONENTS AND PARAMETERS. |  |

|----------|------------------------------------|--|

| IADLUI.  | CIRCUIT COMPONENTS AND TARAMETERS. |  |

| Parameters                                        | Value and Design Selection                                                             |

|---------------------------------------------------|----------------------------------------------------------------------------------------|

| Input voltage $V_{\rm IN}$                        | 100 V                                                                                  |

| Output voltage V <sub>OUT</sub>                   | 5 V                                                                                    |

| Switching frequency                               | 200 kHz                                                                                |

| Transformer turns ratio $n_{\rm P}$ : $n_{\rm S}$ | 4:1                                                                                    |

| Power MOSFETs $S_{\rm P1-2}$                      | 600 V, 29 A, R <sub>DS(on),max</sub> : 99 mΩ,<br>FMC60N099S2A, Fuji Electric           |

| Power MOSFETs $S_{\rm S1-3}$                      | 100 V, 180 A, $R_{DS(on),max}$ : 2.3 m $\Omega$ ,<br>STH315N10F7-6, STMicroelectronics |

| Flying capacitor $C_{\rm FLY}$                    | 264 μF (22 μF x 12), X7R,<br>GRM32ER71E226KE15, Murata                                 |

| Output capacitor $C_0$                            | 264 μF (22 μF x 12), X7R,<br>GRM32ER71E226KE15, Murata                                 |

| Inductor L                                        | 10 µH                                                                                  |

Fig. 9. Measured waveforms of the proposed DPH-SR at  $I_0 = 10$  A.

addition, the inductor DC current  $I_L$  is smaller than  $I_O = 10$  A, confirming the feasibility of the proposed DPH-SR in the ACF converter.

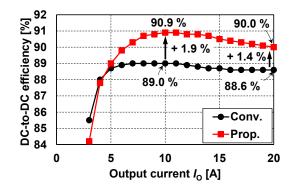

Fig. 10 shows the measured efficiency comparison between the ACF converters with the proposed DPH-SR and conventional SR. The peak efficiency of the proposed DPH-SR and conventional SR is 90.9 % and 89.0 % at  $I_0 = 10$  A, respectively, resulting in the improvement in efficiency by 1.9 %. Furthermore, at  $I_0 = 20$  A, the efficiency is 90.0 % and 88.6 % in the proposed DPH-SR and conventional SR,

Fig. 10. Measured efficiency comparison between the ACF converters with proposed DPH-SR and conventional SR.

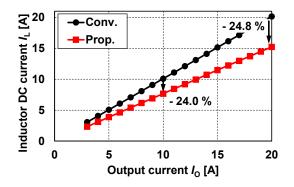

Fig. 11. Measured inductor DC current comparison between the ACF converters with proposed DPH-SR and conventional SR.

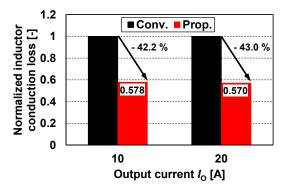

Fig. 12. Normalized inductor conduction loss comparison between the ACF converters with proposed DPH-SR and conventional SR.

respectively, where the efficiency improvement is 1.4 %. These results demonstrate the superiority of the proposed DPH-SR over the conventional SR.

Fig. 11 shows the measured inductor DC current comparison between the ACF converters with the proposed DPH-SR and conventional SR. Although the conventional SR has the almost same  $I_L$  as  $I_O$ , the proposed DPH-SR can reduce  $I_L$  by 24.0 % at  $I_O = 10$  A and 24.8 % at  $I_O = 20$  A. As a result, the inductor conduction loss was drastically reduced by 42.2 % at  $I_O = 10$  A and 43.0 % at  $I_O = 20$  A, as shown in Fig. 12. Consequently, the proposed DPH-SR can improve the efficiency and help to solve the cooling problem of the output inductor in the ACF converter.

#### **IV. CONCLUSIONS**

A dual-path hybrid synchronous rectifier (DPH-SR) in active clamp forward (ACF) converters is proposed for inductor current reduction to solve inductor cooling problems under heavy load. In the measurement, the peak efficiency of the ACF converters with the proposed DPH-SR and conventional SR was 90.9 % and 89.0 % at 10 AOUT, respectively, resulting in the improvement in efficiency by 1.9 %. Furthermore, the efficiency at 20 AOUT was 90.0 % and 88.6 % in the ACF converters with the proposed DPH-SR and conventional SR, respectively, indicating the efficiency is improved by 1.4 %. Then, the proposed DPH-SR can reduce the inductor DC current by 24.8 % at 20 A<sub>OUT</sub> compared to the conventional SR. As a result, the inductor conduction loss of the proposed DPH-SR in the ACF converter was reduced by 43.0 % at 20 A<sub>OUT</sub>. Consequently, the proposed DPH-SR can improve the efficiency and help to solve the cooling problem of the output inductor in the ACF converter.

As future works, detailed design guidelines for active and passive components of ACF converters with the proposed DPH-SR will be proposed. Additionally, parameter optimization such as a dead time, a gate resistance, and an active clamp capacitance will be conducted to improve the converter performance.

#### ACKNOWLEDGMENT

This work was partly supported by JSPS KAKENHI Grant Number 20K14710.

#### REFERENCES

- Q. M. Li, and F. C. Lee, "Design Consideration of the Active-Clamp Forward Converter With Current Mode Control Large-Signal Transient," *IEEE Transactions on Power Electronics*, vol. 18, no. 4, pp. 958–965, Jul. 2003.

- [2] B.-R. Lin, K. Huang, and D. Wang, "Analysis, Design, and Implementation of an Active Clamp Forward Converter With Synchronous Rectifier," *IEEE Transactions on Circuit and Systems I*, vol. 53, no. 6, pp. 1310–1319, Jun. 2006.

- [3] P. Rehlaender, T. Grote, F. Schafmeister and J. Boecker, "Analytical Modeling and Design of an Active Clamp Forward Converter Applied as a Single-Stage On-Board DC-DC Converter for EVs," in Proc. PCIM Europe 2019; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2019, pp. 1–8.

- [4] X. Zhang, B. Nguyen, A. Ferencz, T. Takken, R. Senger and P. Coteus, "A 12- or 48-V Input, 0.9-V Output Active-Clamp Forward Converter Power Block for Servers and Datacenters," *IEEE Transactions on Power Electronics*, vol. 35, no. 2, pp. 1721–1731, Feb. 2020.

- [5] D. Kim, Y. Yamauchi, X. Meng, T. Jia, L. McAuliffe, T. Takken, K. Tien, S. Tian, Y. Yao, A. Ferencz, M. Seok, and X. Zhang, "An Integrated Programmable Gate Timing Control and Gate Driver Chip for A 48V-to-0.75V Active-Clamp Forward Converter Power Block," in *Proc. IEEE Energy Conversion Congress and Exposition (ECCE)*, 2020, pp. 130–134.

- [6] G. Seo and H-P. Le, "S-Hybrid Step-Down DC-DC Converter-Analysis of Operation and Design Considerations," *IEEE Transactions* on *Industrial Electronics*, vol. 67, no. 1, pp. 265–275, Jan. 2020.

- [7] Y. Huh, S. Hong and G. Cho, "A Hybrid Structure Dual-Path Step-Down Converter With 96.2% Peak Efficiency Using 250-mΩ Large-DCR Inductor," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 4, pp. 959–967, April 2019.

- [8] K. Hata, Y. Yamauchi, T. Sai, T. Sakurai, and M. Takamiya, "48V-to-12V Dual-Path Hybrid DC-DC Converter," in *Proc. IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2020, pp. 2279–2284.

- [9] S. Zhen, R. Yang, D. Wu, Y. Cheng, P. Luo and B. Zhang, "Design of Hybrid Dual-Path DC-DC Converter with Wide Input Voltage Efficiency Improvement," in *Proc. IEEE International Symposium on Circuits and Systems (ISCAS)*, 2021, pp. 1–5.

- [10] K. Hata, Y. Jiang, M. -K. Law and M. Takamiya, "Always-Dual-Path Hybrid DC-DC Converter Achieving High Efficiency at Around 2:1 Step-Down Ratio," in *Proc. IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2021, pp. 1302–1307.

- [11] M. Halamicek, T. McRae, N. Vukadinović and A. Prodić, "Modulation Scheme for an Effective Increase in the Number of Levels of DC-DC Multi-Level Flying Capacitor Converters," in *Proc. IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2019, pp. 45– 49.

- [12] Y. Lei, W. Liu and R. C. N. Pilawa-Podgurski, "An Analytical Method to Evaluate and Design Hybrid Switched-Capacitor and Multilevel Converters," *IEEE Transactions on Power Electronics*, vol. 33, no. 3, pp. 2227–2240, March 2018.

- [13] F. Bez, G. Bonanno, L. Corradini and C. Garbossa, "Control technique for reliable operation of the synchronous series capacitor tapped inductor converter," in *Proc. IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2018, pp. 113–120.

- [14] O. Kirshenboim and M. M. Peretz, "High-Efficiency Nonisolated Converter With Very High Step-Down Conversion Ratio," *IEEE Transactions on Power Electronics*, vol. 32, no. 5, pp. 3683–3690, May 2017.

- [15] P. S. Shenoy, M. Amaro, J. Morroni and D. Freeman, "Comparison of a Buck Converter and a Series Capacitor Buck Converter for High-Frequency, High-Conversion-Ratio Voltage Regulators," *IEEE Transactions on Power Electronics*, vol. 31, no. 10, pp. 7006–7015, Oct. 2016.

- [16] Y. Yamauchi, T. Sai, T. Sakurai, and M. Takamiya, "Theoretical and Experimental Analyses of Dynamic Performance of Three-Level Buck Converters in Discontinuous Conduction Mode for Standby Mode Power Supply," *IEEJ Journal of Industry Applications*, vol. 9, no. 3, pp. 271–281, Jan. 2020.