# Demonstration of Efficiency Increase of 350 V-to-13.3 V Isolated DC-DC Converters for Electric Vehicles by Active Gate Driving

Yohei Sukita

The University of Tokyo

Tokyo, Japan

ysukita@iis.u-tokyo.ac.jp

Katsuhiro Hata Shibaura Institute of Technology Tokyo, Japan khata@shibaura-it.ac.jp

Kenichi Nagayoshi Toyota Industries Corporation Aichi, Japan Hiroki Kondo Toyota Industries Corporation Aichi, Japan Kenichi Watanabe Toyota Industries Corporation Aichi, Japan

Makoto Takamiya

The University of Tokyo

Tokyo, Japan

mtaka@iis.u-tokyo.ac.jp

Abstract—An active gate driving (AGD) is applied to a power converter product, and the efficiency increase of the power converter by AGD is demonstrated by measurements under switching noise aligned condition compared to a conventional gate driving. Specifically, the gate driver for a single Si power MOSFET comprising a 165 kHz, 350 V-to-13.3 V isolated DC-DC converter product for electric vehicles was replaced with a developed time-domain stop-and-go active gate driver, and the DC-DC converter efficiency and the spectrum amplitude at 27 MHz of the power MOSFET drain current of the conventional single-step gate driving and the proposed AGD are compared in measurements at 1.2 kW (= 13.3 V, 90 A) output. The results show that the proposed AGD reduces switching loss by 45% compared to the conventional single-step gate driving under the drain current spectrum amplitude alignment condition, resulting in a 10% reduction in total DC-DC converter loss and a 0.9% increase in DC-DC converter efficiency from 90.3% to 91.2%.

Keywords—active gate drive, switching loss, DC-DC converter, efficiency

# I. Introduction

Active gate driving (AGD), which changes the gate driving strength multiple times in fine time slots during the switching period of power devices, is attracting attention as a technology that can solve the trade-off problem between loss and noise during power device switching. Most papers on AGD, however, are limited to measurements of double-pulse tests in half-bridge circuits [1-16], and very few papers have quantitatively demonstrated the advantages of AGD to the whole power converter with measurements [17-19]. Table I shows previous papers that have applied AGD to power converters. In conventional gate driving, which varies the gate resistance, loss and noise during power device switching are in a trade-off relationship. Therefore, to demonstrate the superiority of AGD over the conventional gate driving, it is necessary to either align noise and compare loss or align loss and compare noise. [17] and [18], however, do not show the measured efficiency increase under noise-aligned conditions. [19] shows the measured efficiency increase under noise-aligned conditions, however, it

TABLE I. COMPARISON TABLE OF POWER CONVERTERS WITH AGDs Applied

| Reference                                                            | [17]                                   | [18]                      | [19]                                                            | This work                 |

|----------------------------------------------------------------------|----------------------------------------|---------------------------|-----------------------------------------------------------------|---------------------------|

| Power device                                                         | GaN                                    | IGBT                      | SiC                                                             | Si MOSFET                 |

| Power converter                                                      | Boost converter                        | Buck converter            | 3-phase inverter                                                | Isolated DC-<br>DC        |

| Types of Power<br>Converters                                         | Prototype                              | Prototype                 | Prototype                                                       | Product                   |

| V <sub>IN</sub>                                                      | 12 V (DC)                              | 300 V (DC)                | 282 V (DC)                                                      | 350 V (DC)                |

| V <sub>out</sub>                                                     | 24 V (DC)                              | 50 V (DC)                 | 200 V (AC)                                                      | 13.3 V (DC)               |

| Output power                                                         | NA                                     | 500 to 5 kW               | NA                                                              | 1.2 kW                    |

| Switching<br>frequency                                               | NA                                     | 10 kHz                    | 2 kHz, 20 kHz                                                   | 165 kHz                   |

| Efficiency increase by AGD                                           | Loss: 9.79 W<br>→1.55 W<br>(Simulated) | 92.4%<br>→93.1%<br>(0.7%) | 95.1%→95.4%<br>(0.3%) @ 2 kHz<br>83.9%→85.2%<br>(1.3%) @ 20 kHz | 90.3%<br>→91.2%<br>(0.9%) |

| Types of noise                                                       | V <sub>DS</sub> spectrum               | NA                        | Surge voltage                                                   | I <sub>D</sub> spectrum   |

| Measured efficiency<br>increase under<br>noise-aligned<br>conditions | No                                     | No                        | Yes                                                             | Yes                       |

lacks reality because the power converter is not a commercial product, but a prototype. To solve the problems, in this paper, AGD is applied to a power converter product, and the efficiency increase of the power converter by AGD is demonstrated by measurements under noise-aligned conditions.

### II. TIME-DOMAIN STOP-AND-GO ACTIVE GATE DRIVER

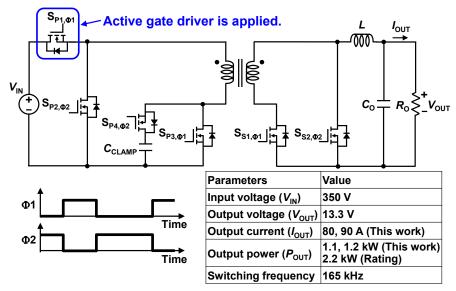

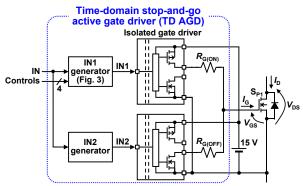

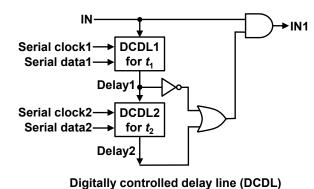

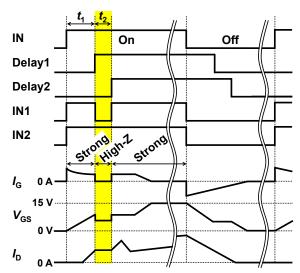

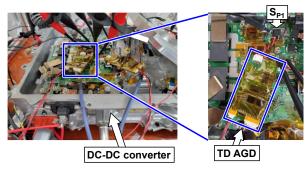

Fig. 1 shows a circuit schematic [20] and specifications of a 350 V-to-13.3 V isolated DC-DC converter product for electric vehicles to which AGD is applied. The time-domain stop-and-go active gate driver (TD AGD) [1-16], which changes the gate driving strength three times from "strong to high-Z to strong", is applied only to the turn-on of Si power MOSFET ( $S_{P1}$ ), which has the largest hard switching loss in the DC-DC converter. Figs. 2 and 3 show the circuit schematic of TD AGD and IN1 generator, which generates  $t_1$  and  $t_2$ , the key parameters determining the performance of TD AGD, respectively. IN2 generator is the dummy delay circuit of IN1 generator. Figs. 4 and 5 show the timing chart and PCB photo of TD AGD, respectively. In the timing chart in Fig. 4, the delay of the

Fig. 1: Isolated DC-DC converter for EVs to which AGD is applied.

Fig. 2: Circuit schematic of TD AGD.

Fig. 3: Circuit schematic of IN1 generator.

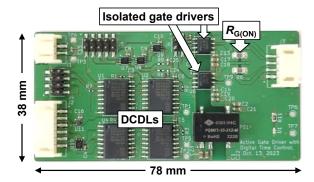

isolated gate drivers and the logic gates is assumed to be zero. As shown in Fig. 4, the first strong drive period after turn-on is defined as  $t_1$ , and the next high-Z drive period as  $t_2$ . TD AGD, implemented with two isolated gate drivers (UCC5320SCDR) and two 8-bit digitally controlled delay lines (DCDLs) (DS1023S-200+), allows  $t_1$  and  $t_2$  to be changed in 2 ns steps

Fig. 4: Timing chart of TD AGD.

Fig. 5: PCB photo of TD AGD.

through digital control signals of "Serial data1" and "Serial data2" in Fig. 3.

Fig. 6: Measurement setup of DC-DC converter.

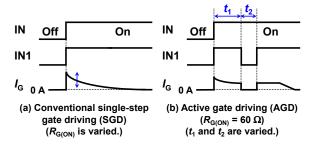

Fig. 7: Timing charts of the conventional SGD and proposed AGD at turnon for comparison.

#### III. MEASURED RESULTS

## A. Measurement Setup

Fig. 6 shows the measurement setup of the DC-DC converter with the gate driver of  $S_{P1}$  modified to TD AGD. The measurements were performed under the conditions shown in Fig. 1. Figs. 8 to 14 show the measured results at output current  $(I_{OUT}) = 90$  A, and Figs. 15 to 17 show the measured results at  $I_{OUT} = 80$  A. In this paper, the performance improvement effect of AGD is investigated in  $I_{OUT}$  range where the DC-DC converter is in hard-switching operation instead of softswitching. Figs. 7 (a) and (b) show timing charts of the conventional single-step gate driving (SGD) and the proposed AGD at turn-on for comparison, respectively. In SGD, the operation is performed by setting  $t_1 = t_2 = 0$  ns in TD AGD and the gate resistance  $R_{G(ON)}$  shown in Fig. 2 is varied in 6 ways from 30 Ω to 200 Ω. In AGD,  $R_{G(ON)} = 60$  Ω is fixed and  $t_1$  and  $t_2$  are varied using DCDLs.

# B. Measured Results at $I_{OUT} = 90 A$

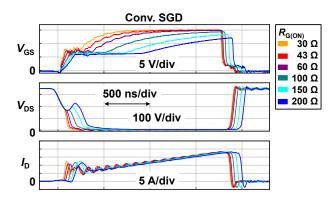

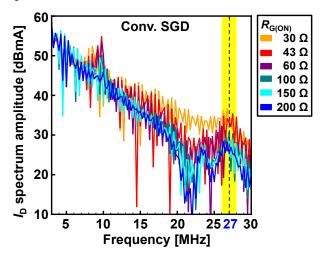

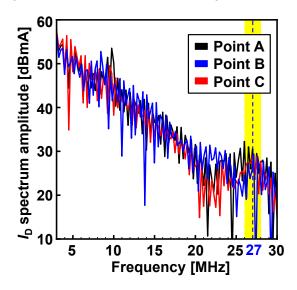

Figs. 8 and 9 show the measured gate-to-source voltage  $(V_{\rm GS})$ , drain-to-source voltage  $(V_{\rm DS})$ , and drain current  $(I_{\rm D})$  waveforms and  $I_{\rm D}$  spectrums of  $S_{\rm Pl}$  in SGD, respectively. Increasing  $R_{\rm G(ON)}$  reduces switching speed of  $S_{\rm Pl}$  (Fig. 8) and  $I_{\rm D}$  spectrum amplitude (Fig. 9). Since peaks of  $I_{\rm D}$  spectrums are observed near 27 MHz in Fig. 9, the maximum value of  $I_{\rm D}$  spectrum amplitude in the range of 26 MHz to 28 MHz is defined as  $I_{\rm D}$  spectrum amplitude at 27 MHz in this paper, and it is used as an index of the switching noise.

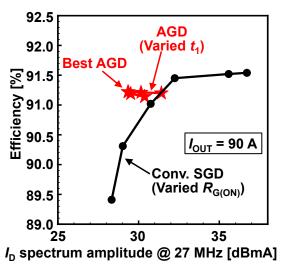

Fig. 10 shows the measured DC-DC converter efficiency vs.  $I_D$  spectrum amplitude of  $S_{P1}$  at 27 MHz in SGD and AGD. The SGD curve is obtained from Figs. 8 and 9. To find the best AGD,  $t_1$  and  $t_2$  of TD AGD are adjusted in 2 ns steps to maximize the

Fig. 8: Measured waveforms of  $S_{P1}$  in SGD at  $I_{OUT} = 90$  A.

Fig. 9: Measured  $I_D$  spectrums of  $S_{P1}$  in SGD at  $I_{OUT} = 90$  A.

efficiency increase of AGD relative to SGD under  $I_D$  spectrum amplitude alignment condition. As an example of  $t_1$ -dependent measured results of AGD, in Fig. 10,  $t_2 = 50$  ns is fixed and  $t_1$  is varied from 90 ns to 98 ns in 2 ns increments. The AGD with  $t_1 = 94$  ns and  $t_2 = 50$  ns is defined as the best AGD.

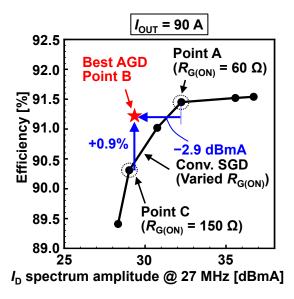

Fig. 11 shows the measured DC-DC converter efficiency vs.  $I_{\rm D}$  spectrum amplitude of S<sub>P1</sub> at 27 MHz in SGD and the best AGD. SGD shows a clear trade-off curve between efficiency and  $I_{\rm D}$  spectrum amplitude. Points A and C are the conventional SGD points with efficiency and  $I_{\rm D}$  spectrum amplitude approximately the same as the best AGD (Point B), respectively. Compared with Points A and C, the best AGD (Point B) increases efficiency by 0.9 % under  $I_{\rm D}$  spectrum amplitude-aligned condition and reduces  $I_{\rm D}$  spectrum amplitude by 2.9 dBmA under efficiency-aligned condition.

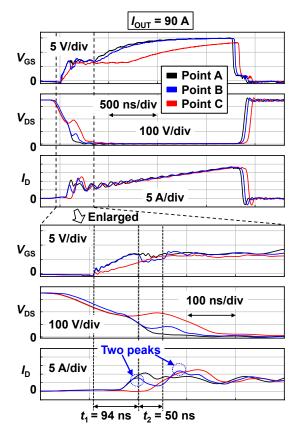

Figs. 12 and 13 show the measured waveforms and  $I_D$  spectrums of Points A to C in Fig. 11 for  $S_{P1}$ , respectively. The best AGD (Point B) with  $t_1 = 94$  ns,  $t_2 = 50$  ns reduces  $I_D$  spectrum amplitude at 27 MHz by splitting the  $I_D$  overshoot into two peaks by inserting  $t_2$  compared to Point A under efficiency-aligned condition. On the other hand, the best AGD (Point B)  $(R_{G(ON)} = 60 \Omega)$  achieves higher efficiency by driving the gate

Fig. 10: Measured DC-DC converter efficiency vs.  $I_D$  spectrum amplitude of  $S_{P1}$  at 27 MHz at  $I_{OUT} = 90$  A. In AGD,  $t_2 = 50$  ns is fixed and  $t_1$  is varied from 90 ns to 98 ns in 2 ns increments.

Fig. 11: Measured DC-DC converter efficiency vs.  $I_{\rm D}$  spectrum amplitude of  $S_{\rm P1}$  at 27 MHz at  $I_{\rm OUT}$  = 90 A.

more strongly with lower  $R_{G(ON)}$  than Point C ( $R_{G(ON)} = 150 \Omega$ ) under  $I_D$  spectrum amplitude-aligned condition.

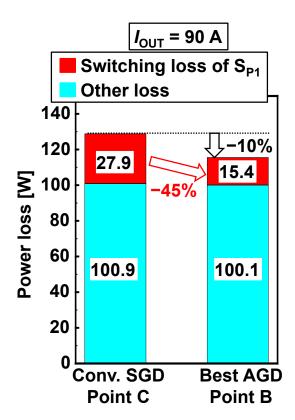

Fig. 14 shows an analysis of the power loss breakdown for Points B and C. Compared to the conventional Point C, the proposed best AGD (Point B) reduces switching losses by 45% from 27.9 W to 15.4 W, resulting in 10% reduction in total DC-DC converter losses from 128.8 W to 115.5 W and a 0.9% increase in converter efficiency from 90.3% to 91.2% under  $I_D$  spectrum amplitude-aligned condition.

# C. Measured Results at $I_{OUT} = 80 A$

To investigate the  $I_{OUT}$  dependence of the parameters  $(t_1, t_2)$  of the best AGD and the performance improvement effect of

Fig. 12: Measured waveforms of Points A to C in Fig. 11 at  $I_{OUT} = 90$  A.

Fig. 13: Measured  $I_D$  spectrums of Points A to C in Fig. 11 at  $I_{OUT} = 90$  A.

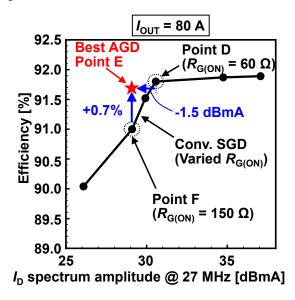

AGD, the measurement results at  $I_{\rm OUT}=80$  A are presented in this section. Fig. 15 shows the measured DC-DC converter efficiency vs.  $I_{\rm D}$  spectrum amplitude of S<sub>P1</sub> at 27 MHz in SGD and the best AGD at  $I_{\rm OUT}=80$  A. The similar AGD performance improvement effect is obtained for  $I_{\rm OUT}=80$  A as for  $I_{\rm OUT}=90$  A (Fig. 11). Points D and F are the conventional SGD points

Fig. 14: Power loss breakdown for Points B and C at  $I_{OUT} = 90$  A.

Fig. 15: Measured DC-DC converter efficiency vs.  $I_{\rm D}$  spectrum amplitude of  $S_{\rm P1}$  at 27 MHz at  $I_{\rm OUT}=80$  A.

with efficiency and  $I_D$  spectrum amplitude approximately the same as the best AGD (Point E), respectively. Compared with Points D and F, the best AGD (Point E) increases efficiency by 0.7 % under  $I_D$  spectrum amplitude-aligned condition and reduces  $I_D$  spectrum amplitude by 1.5 dBmA under efficiency-aligned condition.

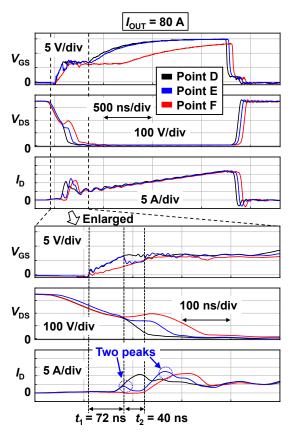

Fig. 16 shows the measured waveforms of Points D to F in Fig. 15 for S<sub>Pl</sub>. In the best AGD,  $(t_1, t_2) = (72 \text{ ns}, 40 \text{ ns})$  at  $I_{\text{OUT}} = 80 \text{A}$  in Fig. 16, while  $(t_1, t_2) = (94 \text{ ns}, 50 \text{ ns})$  at  $I_{\text{OUT}} = 90 \text{A}$  in Fig. 12. Note that  $(t_1, t_2)$  of the best AGD is different for  $I_{\text{OUT}} = 80 \text{ A}$  and 90 A, which suggests that  $(t_1, t_2)$  of AGD needs to be changed depending on  $I_{\text{OUT}}$ . The theory of how to determine  $(t_1, t_2)$  is a future research challenge.

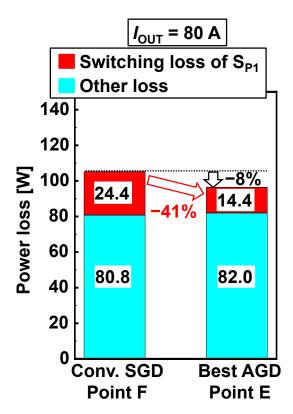

Fig. 17 shows an analysis of the power loss breakdown for Points E and F at  $I_{\rm OUT} = 80$  A. Compared to the conventional Point F, the proposed best AGD (Point E) reduces switching losses by 41% from 24.4 W to 14.4 W, resulting in 8% reduction in total DC-DC converter losses from 105.2 W to 96.4 W and a 0.9% increase in converter efficiency from 91.0% to 91.7% under  $I_{\rm D}$  spectrum amplitude-aligned condition.

#### IV. CONCLUSIONS

TD AGD is applied to the 165 kHz, 350 V-to-13.3 V isolated DC-DC converter product for electric vehicles, and the efficiency increase of the converter by AGD is demonstrated by measurements at 1.2 kW (= 13.3 V, 90 A) output. Compared to the conventional SGD, the proposed TD AGD with  $(t_1, t_2)$  = (94 ns, 50 ns) reduces switching losses by 45% from 27.9 W to 15.4 W, resulting in 10% reduction in total DC-DC converter losses from 128.8 W to 115.5 W and a 0.9% increase in converter efficiency from 90.3% to 91.2% under  $I_D$  spectrum amplitudealigned condition.

Fig. 16: Measured waveforms of Points D to F in Fig. 15 at  $I_{\rm OUT}$  = 80 A.

Fig. 17: Power loss breakdown for Points E and F at  $I_{OUT} = 80$  A.

#### REFERENCES

- [1] V. John, B.-S. Suh, and T. A. Lipo, "High-performance active gate drive for high-power IGBT's," *IEEE Trans. Ind. Appl.*, vol. 35, no. 5, pp. 1108– 1117, Sep-Oct 1999.

- [2] S. Takizawa, S. Igarashi, and K. Kuroki, "A new di/dt control gate drive circuit for IGBTs to reduce EMI noise and switching losses," in PESC 98 Record. 29th Annual IEEE Power Electronics Specialists Conference, 1998, vol. 2, pp. 1443–1449.

- [3] F. Zhang, X. Yang, Y. Ren, L. Feng, W. Chen, and Y. Pei, "Advanced active gate drive for switching performance improvement and overvoltage protection of high-power IGBTs," *IEEE Trans. Power Electron.*, vol. 33, no. 5, pp. 3802–3815, 2018.

- [4] Y. Ling, Z. Zhao, and Y. Zhu, "A self-regulating gate driver for high-power IGBTs," *IEEE Trans. Power Electron.*, vol. 36, no. 3, pp. 3450–3461, 2021.

- [5] A. P. Camacho, V. Sala, H. Ghorbani, and J. L. R. Martinez, "A novel active gate driver for improving SiC MOSFET switching trajectory," *IEEE Trans. Ind. Electron.*, vol. 64, no. 11, pp. 9032–9042, 2017.

- [6] J. Zhu et al., "A 600V GaN active gate driver with dynamic feedback delay compensation technique achieving 22.5% turn-on energy saving," in 2021 IEEE International Solid- State Circuits Conference (ISSCC), 2021, vol. 64, pp. 462–464.

- [7] S. Yu et al., "A 400-V half bridge gate driver for normally-off GaN HEMTs with effective dv/dt control and high dv/dt immunity," IEEE Trans. Ind. Electron., vol. 70, no. 1, pp. 741-751, 2023.

- [8] Y. Sun, L. Sun, A. Esmaeli, and K. Zhao, "A Novel Three Stage Drive Circuit for IGBT," in 2006 1ST IEEE Conference on Industrial Electronics and Applications, 2006, pp. 1–6.

- [9] M. Riefer, J. Winkler, S. Strache, and I. Kallfass, "Implementation of current-source gate driver with open-loop slope shaping for SiC-MOSFETs," in PCIM Europe digital days 2021; International Exhibition

- and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2021, pp. 1–8.

- [10] S. Kawai, T. Ueno, and K. Onizuka, "A 4.5V/ns active slew-rate-controlling gate driver with robust discrete-time feedback technique for 600V superjunction MOSFETs," in 2019 IEEE International Solid-State Circuits Conference (ISSCC), 2019, pp. 252–254.

- [11] Y. Yang, Y. Wen, and Y. Gao, "A novel active gate driver for improving switching performance of high-power SiC MOSFET modules," IEEE Trans. Power Electron., vol. 34, no. 8, pp. 7775–7787, 2019.

- [12] Y. Wen, Y. Yang, and Y. Gao, "Active gate driver for improving current sharing performance of paralleled high-power SiC MOSFET modules," IEEE Trans. Power Electron., vol. 36, no. 2, pp. 1491–1505, 2021.

- [13] M. Sayed, S. Araujo, F. Carraro, and R. Kennel, "Investigation of gate current shaping for SiC-based power modules on electrical drive system power losses," in 2021 23rd European Conference on Power Electronics and Applications (EPE'21 ECCE Europe), 2021, pp. 1–10.

- [14] K. Horii, R. Morikawa, K. Hata, K. Morokuma, Y. Wada, Y. Obiraki, Y. Mukunoki, and M. Takamiya, "Sub-0.5 ns step, 10-bit time domain digital gate driver IC for reducing radiated EMI and switching loss of SiC MOSFETs," in 2022 IEEE Energy Conversion Congress and Exposition (ECCE), 2022, pp. 1–8.

- [15] D. Zhang, K. Horii, K. Hata, and M. Takamiya, "Digital gate driver IC with fully integrated automatic timing control function in stop-and-go gate drive for IGBTs," in 2023 IEEE Applied Power Electronics Conference and Exposition (APEC), 2023, pp. 1225–1231.

- [16] D. Zhang, K. Horii, K. Hata, and M. Takamiya, "Digital gate driver IC with real-time gate current change by sensing drain current to cope with operating condition variations of SiC MOSFET," in 2023 11th International Conference on Power Electronics and ECCE Asia (ICPE 2023 ECCE Asia), 2023, pp. 374–380.

- [17] C. Krause and S. Frei, "Narrowband frequency domain optimized gate driving signals for power transistors of DC/DC converters," in 2023 International Symposium on Electromagnetic Compatibility – EMC Europe, 2023, pp. 1–6.

- [18] G. Zhang, B. J. Zhang, S. Shao, and W. Qu, "A load adaptive intelligent IGBT gate drive," in 2023 11th International Conference on Power Electronics and ECCE Asia (ICPE 2023 - ECCE Asia), 2023, pp. 3294– 3299

- [19] V.-L. Pham, H. Obara, and K. Hata, "A partial active gate control for improvement of a trade-off relation between surge voltage and efficiency in a three-phase inverter," IEEE Trans. Ind. Appl., vol. 60, no. 3, pp. 4239–4250, May-June 2024.

- [20] K. Watanabe, "DC-DC converter," Japanese patent, P2020-202679A, Dec. 17, 2020.